# ACS APPLIED MATERIALS & INTERFACES

# Sidewall Crystalline Orientation Effect of Post-treatments for a Replacement Metal Gate Bulk Fin Field Effect Transistor

Jae Woo Lee,<sup>\*,†,‡</sup> Eddy Simoen,<sup>†</sup> Anabela Veloso,<sup>†</sup> Moon Ju Cho,<sup>†</sup> Guillaume Boccardi,<sup>†</sup> Lars-Åke Ragnarsson,<sup>†</sup> Thomas Chiarella,<sup>†</sup> Naoto Horiguchi,<sup>†</sup> Guido Groeseneken,<sup>†,‡</sup> and Aaron Thean<sup>†</sup>

<sup>†</sup>Imec, 3001 Leuven, Belgium

<sup>‡</sup>Katholieke Universiteit Leuven, 3001 Leuven, Belgium

**ABSTRACT:** The crystalline orientation effect is investigated for post-treatments of a replacement metal gate (RMG) p-type bulk fin field effect transistor (FinFET). After post-deposition annealing (PDA) and SF<sub>6</sub> plasma treatment, the hole mobility is improved. From low-frequency noise analysis, reduction of the trap density and noise level is observed in PDA- and SF<sub>6</sub>plasma-treated devices. (100) sidewall-oriented FinFETs show a lower noise level because of fewer interface traps compared to (110) sidewall-oriented devices. SF<sub>6</sub> plasma affects the interface traps, whereas PDA relatively more affects bulk oxide traps for RMG high-*k* last FinFET.

KEYWORDS: FinFET, crystalline orientation, low-frequency noise, replacement metal gate, post-deposition annealing, SF<sub>6</sub> plasma

## 1. INTRODUCTION

The high-k/metal gate (HK/MG) has played an important role in the downscaling of complementary metal—oxide semiconductor technology. Recently, the replacement metal gate (RMG) scheme has been introduced.<sup>1,2</sup> In the RMG high-k last scheme, a dummy poly-Si/SiO<sub>2</sub> gate stack is etched away and replaced by HK/MG after junction formation and dopant activation. Therefore, an aggressive thermal budget for the HK/ MG stacks can be avoided using RMG integration. However, the oxide etching and following HK/MG stack induce additional interface states and degrade the device performance.<sup>3</sup> To improve the quality of the RMG HK/MG stack, additional post-treatment is necessary such as post-deposition annealing (PDA) or SF<sub>6</sub> plasma treatment.<sup>4,5</sup>

Implementation of the RMG scheme for a fin field effect transistor (FinFET) is more complicated. Because of the threedimensional channel structure of a FinFET, the surface property of the fin sidewall is different from that of the top surface of the fin. The etching process for fin formation induces higher surface roughness and interfacial states on fin sidewalls.<sup>6</sup> Additionally, FinFETs can be fabricated with either a (110) or (100) crystalline orientation of the sidewall surface. Because carrier transport on the sidewall becomes dominant at narrow fin width, the study of the fin sidewall orientation is very important.<sup>7</sup>

In this paper, the performance improvement of high-k last ptype bulk FinFET using PDA and SF<sub>6</sub> plasma treatment is investigated based on the different crystalline orientations of the fin sidewall. Using low-frequency noise analysis, the noise level and trap density profile are compared for each posttreatment scheme.

# 2. EXPERIMENTAL SECTION

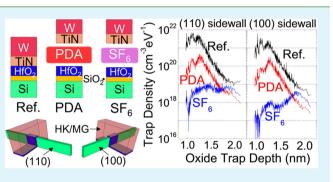

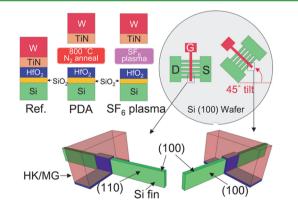

Two different post-treated high-*k* last FinFETs (PDA and SF<sub>6</sub> plasma) are prepared with nothing-treated high-*k* last FinFET references for each of the (110) and (100) sidewall orientations. The fin channel structure is patterned on a (100) surface-oriented 300 mm silicon wafer and doped before a Si/SiO<sub>2</sub> dummy gate stack deposition. (100) sidewall-surface-oriented FinFET is fabricated by 45° rotation of (110) sidewall-surface-oriented FinFET, as shown in Figure 1. After halo and

**Figure 1.** Schematics of RMG high-*k* last gate stacks for bulk FinFET with different fin sidewall orientations. Three different post-treatment schemes (untreated reference, PDA, and  $SF_6$  plasma) are used after HfO<sub>2</sub> deposition.

Received: August 7, 2013 Accepted: September 5, 2013 Published: September 5, 2013

ACS Publications © 2013 American Chemical Society

8865

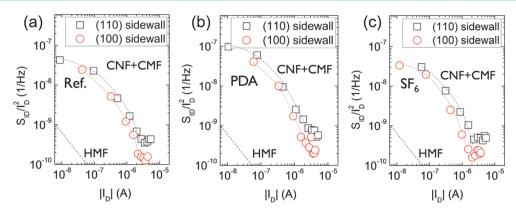

**Figure 2.** Normalized drain current noise power spectral density at 50 Hz and  $V_D = -50$  mV for (a) untreated reference and (b) PDA- and (c) SF<sub>6</sub>plasma-treated FinFETs with different sidewall surface orientations. Low-frequency noise behavior is well matched with the CNF+CMF model. (100) sidewall-surface-oriented FinFETs show lower noise levels for all post-treatment schemes.

Table 1. Summary of Device Parameters According to the Different Post-treatment Schemes and Fin Sidewall Orientations for  $W_{\text{fin}} = 20 \text{ nm}$ ,  $H_{\text{fin}} = 30 \text{ nm}$ , and  $L_{\text{G}} = 1 \ \mu \text{m}$  at 50 Hz

|                                                       | sidewall orientation, post-treatment |                        |                               |                        |                        |                               |

|-------------------------------------------------------|--------------------------------------|------------------------|-------------------------------|------------------------|------------------------|-------------------------------|

|                                                       | (110), reference                     | (110), PDA             | (110), SF <sub>6</sub> plasma | (100), reference       | (100), PDA             | (100), SF <sub>6</sub> plasma |

| peak of effective mobility $(cm^2/V{\cdot}s)$         | 146                                  | 151                    | 156                           | 80                     | 91                     | 108                           |

| $AS_{\rm VG}f\left(\mu{\rm m}^2\cdot{\rm V}^2\right)$ | $6.36 \times 10^{-10}$               | $1.76 \times 10^{-10}$ | $2.63 \times 10^{-10}$        | $2.68 \times 10^{-10}$ | $1.26 \times 10^{-10}$ | $1.38 \times 10^{-10}$        |

| $N_{\rm t}~({\rm cm}^{-3}{\cdot}{\rm eV}^{-1})$       | $8.04 \times 10^{19}$                | $1.91 \times 10^{19}$  | $2.27 \times 10^{19}$         | $3.38 \times 10^{19}$  | $1.37 \times 10^{19}$  | $1.50 \times 10^{19}$         |

| $\alpha$ (V·s/C)                                      | $1.21 \times 10^{4}$                 | $2.22 \times 10^{4}$   | $1.44 \times 10^{5}$          | $1.7 \times 10^{4}$    | $3.25 \times 10^{4}$   | $1.53 \times 10^{5}$          |

| EOT (nm)                                              | 0.77                                 | 0.83                   | 0.83                          | 0.70                   | 0.70                   | 0.73                          |

source/drain (S/D) extensions are doped and spacers are formed, the RMG module is implemented. First, the Si/SiO<sub>2</sub> dummy gate stack is chemically etched. Then, the interfacial layer oxide is grown using O<sub>3</sub> oxidation and a 1.8 nm HfO<sub>2</sub> high-*k* layer is deposited using atomic layer deposition. For improvement of the HK/MG stack, PDA at 800 °C during 1 s or radio-frequency-power-induced SF<sub>6</sub> plasma during 9 min is employed. SF<sub>6</sub> plasma with argon as an inert gas was optimized to increase the number of ions reaching the bottom of the narrow trench effectively. Finally, gate metal is deposited, and S/D silicidation is carried out. In this study, the device dimensions are fixed as fin width  $W_{\rm fin} = 20$  nm, fin height  $H_{\rm fin} =$ 30 nm, and gate length  $L_{\rm G} = 1 \ \mu$ m.

A BTA 9812 noise analyzer is used for the low-frequency noise measurement. All noise measurements were carried out under  $V_{\rm D}$  = -50 mV for the linear operation regime.

## 3. RESULTS AND DISCUSSION

In Figure 2, the sidewall orientation comparisons of normalized drain current noise power spectral density  $S_{\rm ID}/I_{\rm D}^2$  at 50 Hz are shown for the untreated reference (Figure 2a) and PDA-treated (Figure 2b) and SF<sub>6</sub>-plasma-treated (Figure 2c) FinFETs. The low-frequency noise mechanism can be modeled by two well-known approaches: (i) the carrier number + correlated mobility fluctuation (CNF+CMF) model based on carrier trapping and detrapping near the dielectric/semiconductor interface and associated mobility fluctuations due to Coulomb scattering. In the CNF+CMF model,  $S_{\rm ID}/I_{\rm D}^2$  mainly follows  $(g_{\rm m}/I_{\rm D})^2$  shape<sup>8,9</sup>

$$\frac{S_{\rm ID}}{I_{\rm D}^2} = (1 + \alpha \mu_{\rm eff} C_{\rm ox} I_{\rm D} / g_{\rm m})^2 S_{\rm Vfb} \left(\frac{g_{\rm m}}{I_{\rm D}}\right)^2 \tag{1}$$

where  $\alpha$  is the Coulomb scattering parameter relevant to mobility fluctuation (V·s/C),  $\mu_{\rm eff}$  the effective mobility (cm<sup>2</sup>/V· s),  $C_{\rm ox}$  the oxide capacitance per unit area (F/cm<sup>2</sup>),  $g_{\rm m}$  the transconductance [= $\delta I_{\rm D}/\delta V_{\rm G}$  (A/V)],  $S_{\rm Vfb}$  the flat-band voltage power spectrum (V<sup>2</sup>/Hz). In contrast, (ii) the Hooge mobility fluctuation (HMF) model is based on the carrier mobility fluctuation by phonon interaction.  $S_{\rm ID}/I_{\rm D}^2$  is proportional to  $I_{\rm D}^{-1}$  in the HMF model<sup>8,9</sup>

$$\frac{S_{\rm ID}}{I_{\rm D}^2} = \frac{\alpha_{\rm H}}{Nf} \propto \frac{1}{I_{\rm D}}$$

(2)

where  $\alpha_{\rm H}$  is the Hooge constant and  $N_{\rm c}$  the total carrier number. Figure 2 clearly shows that the low-frequency noise of RMG high-*k* last FinFETs is based on the CNF+CMF model affected by carrier trapping/detrapping events.

For all cases in Figure 2, the (100) sidewall shows lower  $S_{\rm ID}/I_{\rm D}^2$  trends due to relatively lower interface traps on the (100) sidewall surface. Because the number of Si atoms per unit area on the (110) surface is approximately 1.4 times higher than that on the (100) surface, (110) sidewall-oriented FinFETs have a higher density of dangling bonds than (100) sidewall-oriented FinFETs, resulting in an increased trap density near the Si/SiO<sub>2</sub> interface.<sup>10,11</sup>

Because the low-frequency noise mechanism of RMG FinFETs originates from carrier trapping/detrapping, the tunneling depth dependence of the trap density can be calculated. The oxide trap depth z is converted from the frequency information according to<sup>9,12,13</sup>

$$z = \lambda \ln \left( \frac{1}{2\pi f \tau_0} \right) \tag{3}$$

with  $\tau_0$  the tunneling time constant, which is approximately  $10^{-10}$  s, and  $\lambda$  the oxide tunneling distance at approximately

$10^{-8}$  cm. The oxide trap density  $N_{\rm t}$  can be calculated from  $S_{\rm Vfb}$  affected by charge trapping and detrapping based on the tunneling process into the gate oxide<sup>8</sup>

$$S_{\rm Vfb} = \frac{q^2 k_{\rm B} T \lambda N_{\rm t}}{f W L C_{\rm ox}^2} \tag{4}$$

where *q* is the electric charge,  $k_{\rm B}$  the Boltzmann constant, *T* the temperature, *f* the frequency, *W* the total channel width ( $W_{\rm fin}$  +  $2H_{\rm fin}$ ), and *L* the channel length.

The  $N_{\rm t}$  values are calculated by fitting eqs 1 and 4 to  $S_{\rm ID}/I_{\rm D}^{-2}$ .  $\mu_{\rm eff}$  and  $C_{\rm ox}$  were estimated using the split C-V method.<sup>14</sup> The device parameters for the fitting are shown in Table 1. As shown in Table 1, higher hole effective mobility in the (110) fin sidewall surface is generally shown compared to the (100) sidewall surface. Higher hole mobility in the (110) surface than the (100) surface has been reported.<sup>7,15–17</sup> Generally, the (110) silicon surface orientation has a lighter hole effective mass than (100) because of the hole effective mass anisotropy in different silicon surface orientations, and it makes the effective mobility higher. In the FinFET with a narrow fin width, the sidewall surface orientation is dominant for carrier transport. Thus, the FinFET with the (110) sidewall surface has higher mobility than that with the (100) sidewall surface orientation.

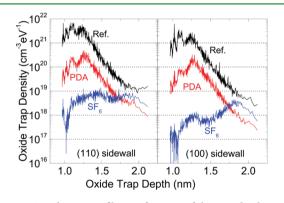

Figure 3 shows the oxide trap density profiles as a function of the oxide trap depth at  $V_{\rm G} = V_{\rm T}$ . For both (110) and (100)

**Figure 3.** Trap density profile as a function of the trap depth at  $V_{\rm G} = V_{\rm T}$ . SF<sub>6</sub>-plasma-treated devices have the lowest trap density near the interface, whereas PDA-treated devices have lower bulk oxide traps at high oxide trap depth. Each post-treatment condition of (100) sidewall FinFETs has lower trap density profiles compared to those of (110) sidewall FinFETs.

sidewall-oriented FinFETs, PDA- and SF<sub>6</sub>-plasma-treated devices have reduced trap densities compared to the references. It is clearly shown that the SF<sub>6</sub>-plasma-treated devices show lower traps near the interface. In contrast, PDA-treated devices show lower traps in the bulk oxide region. PDA-treated devices show that the high trap density near the interface exponentially decreases in the bulk oxide region, whereas the trap densities of SF<sub>6</sub>-plasma-treated devices gradually increase or become saturated as the trap depth increased.

Previously, the effect of PDA and SF<sub>6</sub> plasma treatments has been reported for planar devices. The PDA treatment reduces the oxygen vacancies in the HfO<sub>2</sub> layer.<sup>18,19</sup> During PDA treatment, the oxygen vacancies are passivated by nitrogen in bulk oxide. In the study of SF<sub>6</sub> plasma treatment, interface trap passivation by Hf–F and Si–F bonds has been shown.<sup>20,21</sup>

In Figure 3, the SF<sub>6</sub>-plasma-treated device shows approximately 1 decade difference between (110) and (100) sidewalloriented FinFETs near the interface, whereas reference and PDA-treated devices show relatively small differences (2–3 times). It seems that the SF<sub>6</sub> plasma treatment gives a more interface state dominant effect compared to the PDA treatment. Near the interface, the trap density profile depends on the interface traps. Higher dangling bonds on the (110) sidewall induce higher interface traps compared to the (100) sidewall surface. Thus, the higher sidewall surface orientation dependence of the SF<sub>6</sub> plasma treatment near the interface means more interface trap passivation effect of the SF<sub>6</sub> plasma treatment for RMG FinFET.

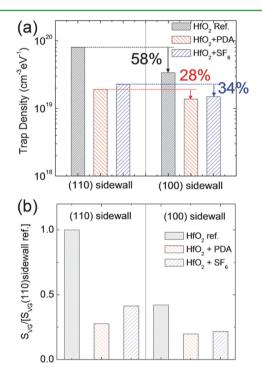

Figure 4a shows bulk oxide trap densities estimated at 50 Hz and different sidewall surface orientations for each post-

**Figure 4.** (a) Trap density at 50 Hz and (b) input-referred voltage noise normalized by the (110) reference. PDA and  $SF_6$  plasma treatment reduces the traps and noise level. Both parts a and b shows that the  $SF_6$  plasma treatment is more surface-orientation-dependent.

treatment scheme. At the (100) sidewall surface, the untreated reference shows 58% reduced trap density compared to the (110) sidewall-oriented one. For PDA and SF<sub>6</sub> plasma treatment, 28% and 34% reductions are shown respectively at (100) sidewall FinFETs. Even though the untreated reference shows the most reduced trap density at the (100) sidewall, it still has the highest trap density compared to the PDA and SF<sub>6</sub> plasma treatment options at the same sidewall orientation.

In Figure 4b, the input-referred noise  $S_{VG}$  ( $S_{VG} = S_{ID}/g_m^2$ ) is compared at 50 Hz and  $V_G = V_T$ . Each  $S_{VG}$  is normalized by the date for the untreated reference with the (110) sidewall for quantitative comparison. All (100) sidewall-oriented FinFETs show reduced  $S_{VG}$  values compared to (110) sidewall devices. Whereas the SF<sub>6</sub>-plasma-treated device has 1.51 times higher  $S_{VG}$  than the PDA-treated one at the (110) sidewall surface, it is 1.09 times higher for the SF<sub>6</sub> plasma compared to the PDA option at the (100) sidewall surface. The crystalline orientation of the fin sidewall seems more effective for SF<sub>6</sub> plasma posttreatment, which means that SF<sub>6</sub> plasma affects more interface traps. At the (100) sidewall FinFET, the SF<sub>6</sub> plasma post-

## **ACS Applied Materials & Interfaces**

treatment option has the advantage of low-frequency noise and interface trap compared to the other options and improved low-frequency noise similar to PDA-treated FinFETs.

#### 4. CONCLUSION

In conclusion, PDA and SF<sub>6</sub> plasma post-treatments have been studied for the RMG high-*k* last p-type bulk FinFETs according to the different sidewall orientations. In the RMG high-*k* scheme, PDA and SF<sub>6</sub> post-treatments reduce the lowfrequency noise and trap density. (100) sidewall-surfaceoriented devices show lower noise and trap density for all post-treatment schemes compared to (110) sidewall FinFETs. The SF<sub>6</sub> plasma treatment relatively more affects the interface traps, whereas PDA more affects bulk oxide traps for the RMG HK/MG stack.

## AUTHOR INFORMATION

## **Corresponding Author**

\*E-mail: jaewoo@imec.be.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The Imec Core Partners are gratefully acknowledged for their financial support of the Logic Device Program.

## REFERENCES

(1) Boccardi, G.; Ritzenthaler, R.; Togo, M.; Chiarella, T.; Kim, M.; Yuichiro, S.; Veloso, A.; Chew, S. A.; Vecchio, E.; Locorotondo, S.; Deyriendt, K.; Ong, P.; Brus, S.; Horiguchi, N.; Thean, A. *Proc. Int. Conf. Solid State Device Mater.* **2012**, 723–724.

(2) Hyun, S.; Han, J.; Park, H.; Na, H.; Son, H. J.; Lee, H. Y.; Hong, H.; Lee, H.; Song, J.; Kim, J. J.; Lee, J.; Jeong, W. C.; Cho, H. J.; Seo, K. I.; Kim, D. W.; Sim, S. P.; Kang, S. B.; Sohn, D. K.; Siyoung, C.; Kang, H.; Chilhee, C. *Proceedings of VLSI Technology (VLSIT), 2011 Symposium*, June 14–16, 2011; IEEE: New York, 2011; pp 32 and 33.

(3) Lee, J. W.; Cho, M. J.; Simoen, E.; Ritzenthaler, R.; Togo, M.; Boccardi, G.; Mitard, J.; Ragnarsson, L.-A.; Chiarella, T.; Veloso, A.; Horiguchi, N.; Thean, A.; Groeseneken, G. *Appl. Phys. Lett.* **2013**, *102*, 073503.

(4) Chen, Y.-T.; Fu, S.-I.; Lin, C.-T.; Chiang, W.-T.; Chang, S.-J.; Lin, M.-S.; Jenq, J.-S. J. Vac. Sci. Technol., B 2013, 31, 020604.

(5) Lee, J. W.; Simoen, E.; Veloso, A.; Cho, M. J.; Arimura, H.; Boccardi, G.; Ragnarsson, L. K.; Chiarella, T.; Horiguchi, N.; Thean, A.; Groeseneken, G. *IEEE Trans. Electron Devices* **2013**, *60*, 2960–2962.

(6) Lee, J. W.; Jang, D.; Mouis, M.; Kim, G. T.; Chiarella, T.; Hoffmann, T.; Ghibaudo, G. Solid-State Electron. **2011**, 62, 195–201.

(7) Young, C. D.; Akarvardar, K.; Baykan, M. O.; Matthews, K.; Ok, I.; Ngai, T.; Ang, K. W.; Pater, J.; Smith, C. E.; Hussain, M. M.; Majhi,

P.; Hobbs, C. Solid-State Electron. 2012, 78, 2-10.

(8) Ghibaudo, G.; Boutchacha, T. Microelectron. Reliab. 2002, 42, 573-582.

(9) Von Haartman, M.; Östling, M. Low-frequency noise in advanced MOS devices; Springer: Dordrecht, The Netherlands, 2007.

(10) Po Chin, H.; San Lein, W.; Shoou-Jinn, C.; Yao Tsung, H.; Chen, J. F.; Chien-Ting, L.; Ma, M.; Cheng, O. *IEEE Trans. Electron Devices* **2011**, *58*, 1635–1642.

(11) Kapila, G.; Kaczer, B.; Nackaerts, A.; Collaert, N.; Groeseneken, G. V. *IEEE Electron Device Lett.* **2007**, *28*, 232–234.

(12) Crupi, F.; Giusi, G.; Iannaccone, G.; Magnone, P.; Pace, C.; Simoen, E.; Claeys, C. J. Appl. Phys. **2009**, 106, 073710.

(13) Hung, K. K.; Ko, P. K.; Chenming, H.; Cheng, Y. C. *IEEE Trans. Electron Devices* **1990**, *37*, 654–665.

(14) Romanjek, K.; Andrieu, F.; Ernst, T.; Ghibaudo, G. IEEE Electron Device Lett. 2004, 25, 583-585.

(15) Yang, M.; Gusev, E. P.; Ieong, M. K.; Gluschenkov, O.; Boyd, D. C.; Chan, K. K.; Kozlowski, P. M.; D'Emic, C. P.; Sicina, R. M.; Jamison, P. C.; Chou, A. I. *IEEE Electron Device Lett.* **2003**, *24*, 339–341.

(16) Mehrotra, S.; Paul, A.; Luisier, M.; Klimeck, G. Proceedings of Microelectronics and Electron Devices. WMED 2009. IEEE Workshop, April 3, 2009; IEEE: New York, 2009; pp 1–4.

(17) Mereu, B.; Rossel, C.; Gusev, E. P.; Yang, M. J. Appl. Phys. 2006, 100, 014504.

(18) Park, H.; Jo, M.; Choi, H.; Hasan, M.; Choi, R.; Kirsch, P. D.; Kang, C.-Y.; Lee, B.-H.; Kim, T.-W.; Lee, T.; Hwang, H. *IEEE Electron Device Lett.* **2008**, *29*, 54–56.

(19) Ong, Y. C.; Ang, D. S.; O'Shea, S. J.; Pey, K. L.; Wang, S. J.; Tung, C. H.; Li, X. J. Appl. Phys. **2008**, 104, 064119.

(20) Wang, Y.; Chen, Y.-T.; Zhao, H.; Xue, F.; Zhou, F.; Lee, J. C. *Appl. Phys. Lett.* **2011**, *98*, 043506.

(21) Ma, T. P. J. Vac. Sci. Technol., A 1992, 10, 705-712.